### Medidas no Chip Teste Fabricado

## 1.1) Diodo pn

#### a) Fator de idealidade:

Pelas considerações feitas no estudo de diodos no chip didático, o fator de idealidade  $\eta$  é obtido do coeficiente angular da expressão  $I_D = I_0 \exp\left(\frac{qV_D}{\eta kT}\right)$  linearizada, expressão aproximada para  $V_D > 100$  mV:

$$\log(I_D) = \frac{q \cdot \log e}{\eta kT} V_D + \log(I_0)$$

$$\eta = \frac{1}{\alpha} \cdot \frac{q \log e}{kT}$$

Dessa forma, utilizando o analisador de parâmetros HP4145B, trace as curvas  $I_D \times V_D$  e  $\log(I_D) \times V_D$ . Para isto, conecte o catodo (lado n) com o canal SMU que corresponde ao terminal comum; quanto ao anodo (lado p), conecte-o com o canal que corresponde à var1.

Da curva  $\log(I_D)$  x  $V_D$ , tome dois pontos na região  $0.1 \le V_D \le 0.3$  V e obtenha o coeficiente angular  $\alpha$ . Na seqüência, calcule o fator de idealidade  $\eta$ :

$$\alpha =$$

$$\eta =$$

Comente os resultados obtidos.

#### b) Tensão de ruptura BV

Para verificar o comportamento do diodo na região reversa e encontrar o valor da tensão de rompimento ( $Breakdown\ Voltage\ BV$ ), utilize o analisador de parâmetros, atentando para o limite do equipamento de +/-100V.

$$BV[V] =$$

Comente o resultado.

#### c) Estudo na região reversa

Neste item, meça o valor da corrente reversa para  $|V_D| = 5$  V. Compare este valor com os valores obtidos em outros dispositivos e com o das outras lâminas processadas.

Comente sobre o valor obtido.

## 1.2) Capacitor MOS

- a) Obtenha a curva Capacitância x Tensão para o capacitor MOS, calcule os parâmetros indicados a seguir e comente os resultados obtidos.

- espessura do óxido (t<sub>ox</sub>)

$$t_{ox} = \frac{\epsilon_{o}.\epsilon_{ox}.A}{C_{ac}}$$

$$\epsilon_{o} = 8.854 \text{ x 10-14 Faraday/centímetro}$$

$$\epsilon_{ox} = 3.9 \text{ (para S}_{i}O_{2})$$

$$A \Rightarrow \text{Área do capacitor em cm}^{2}$$

$$C_{ac} \Rightarrow \text{Capacitância na região de acumulação}$$

$$t_{ox} = 0$$

• largura da camada de depleção (W<sub>f</sub>)

$$W_{_{f}} = \begin{bmatrix} \frac{C_{_{ac}}}{C_{_{inv}}} - 1 \end{bmatrix} \cdot \frac{\epsilon_{_{0}}.\epsilon_{_{Si}}.A}{C_{_{ac}}} \qquad \begin{array}{c} \epsilon_{Si} = 11.9 \\ C_{_{inv}} \Rightarrow Capacitância na região de inversão \end{array}$$

$$W_{\mathrm{f}} =$$

• concentração de portadores (N<sub>A,D</sub>)

$$N_{A,D} \big( n+1 \big) = \frac{4.\epsilon_0.\epsilon_{Si}}{q.W_f^2} \cdot \left( \frac{kT}{q} \right) ln \left[ \frac{N_{A,D}(n)}{n_i} \right] \hspace{0.5cm} \text{C\'alculo recursivo}$$

| $N_{A,D}(0) = 10^{15} \implies$ | $N_{A,D}$     | $N_{A,D}(1) =$ |  |

|---------------------------------|---------------|----------------|--|

| $N_{A,D}(1) =$                  | $\Rightarrow$ | $N_{A,D}(2) =$ |  |

| $N_{A,D}(2) =$                  | $\Rightarrow$ | $N_{A,D}(3) =$ |  |

| $N_{A,D}(3) =$                  | $\Rightarrow$ | $N_{A,D}(4) =$ |  |

• capacitância de "flat-band"

$$C_{\text{FB}} = \frac{\epsilon_{\text{o}}.\epsilon_{\text{Si}}.A}{t_{\text{ox}} + \frac{\epsilon_{\text{ox}}}{\epsilon_{\text{Si}}} \left[ \frac{\epsilon_{\text{o}}.\epsilon_{\text{Si}}}{q.N_{\text{A,D}}} \left( \frac{kT}{q} \right) \right]^{\frac{1}{2}}}$$

$k = 8.62 \times 10^{-5}$  eletron-Volt/Kelvin  $T \Rightarrow$  Temperatura  $q = 1.602 \times 10^{-19}$  Coulomb

$$C_{FB} =$$

• cargas efetivas de interface (Q<sub>ef</sub>/q)

$$\phi_{MS} = -0.6 - \phi_{F}$$

, onde

$$\phi_{F} = \left(\frac{kT}{q}\right) \ln \left[\frac{N_{A,D}}{n_{i}}\right] e$$

$$\phi_F > 0 \Rightarrow \text{tipo p}$$

$$\phi_F < 0 \Rightarrow \text{tipo n}$$

$n_i$ = 1,45 x  $10^{10}$  e  $V_{FB}$  é a tensão onde a capacitância é igual à  $C_{FB}$ , obtida através da curva C x V

$$egin{aligned} V_{FB} = \ & \Phi_F = \ & \Phi_{MS} = \ \end{aligned}$$

$$\frac{Q_{\text{ef}}}{q} = \! \big[ V_{\text{FB}} - \! \varphi_{\text{MS}} \big] \! . \frac{C_{\text{ac}}}{q.A} \label{eq:qef}$$

$$Q_{\rm ef}\!/q =$$

# 1.3) Transistores MOSFET

- a) Utilizando o HP4145B, obtenha as curvas características ( $I_D \times V_{DS}$ ) de 2 transistores da lâmina, um de canal curto e um de canal longo. Explique o porquê de seu formato, indicando as regiões ôhmica e de saturação e compare as curvas dos 2 transistores.

- b) Obtenha a curva  $I_D$  x  $V_{GS}$  para  $|V_{DS}| = 0,1$  e  $|V_{BS}| = 0,2$  e 4V. Determine valor de  $V_{T0}$ , mobilidade ( $\mu$ ) e fator de corpo ( $\gamma$ ) e comente os resultados obtidos.

$$V_{T0} =$$

$$\mu = \frac{L_{\text{eff}} \cdot A \cdot gm}{W \cdot C_{\text{ac}} \cdot V_{\text{DS}}}, \text{ onde } L_{\text{eff}} = L - 1.4 \text{ X}_{\text{J}}$$

$L \Rightarrow$  comprimento do canal

$X_J \Rightarrow$  profundidade da junção

$W \Rightarrow largura do canal$

$C_{ac}$ ,  $A \Rightarrow$  parâmetros obtidos na medida  $C \times V$

gm ⇒ transcondutância máxima

$$\mu =$$

$$\gamma = \frac{A}{C_{ac}} \sqrt{2q\epsilon_{Si}\epsilon_0 N_{A,D}}$$

$C_{ac}$ , A,  $N_{A,D}$   $\Rightarrow$  parâmetros obtidos na medida C x V

$\varepsilon_{Si} = 11.9$

$\varepsilon_0 = 8.854 \text{ x } 10\text{-}14 \text{ Faraday/centímetro}$

$q = 1.602 \text{ x } 10^{-19} \text{ Coulomb}$

$\gamma =$

- c) Obtenha a curva  $\sqrt{I_D}$  x  $V_{GS}$ , com  $V_{DS} = V_{GS}$  e  $V_{BS} = 0V$ . Encontre o valor de  $V_{T0}$  e compare com o valor encontrado anteriormente. Qual método é mais preciso na determinação de  $V_{T0}$ ?

- d) Obtenha as curvas  $I_D$  x  $V_{GS}$  em região sub-limiar, com  $|V_{DS}|=1$ , 2 e 3,9 V, e  $V_{BS}=0$ V. Determine o fator de idealidade e explique o formato das curvas obtidas.

n =

# 1.4) Cruz Grega

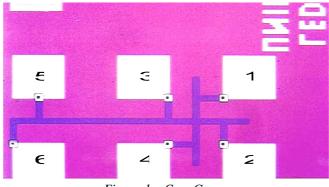

O estudo de resistências no chip fabricado se dá através da estrutura intitulada como "Cruz Grega", cuja estrutura é mostrada abaixo.

Figura 1 – Cruz Grega

A obtenção da resistência por quadrado é possível medindo-se a queda de tensão entre 2 e 4, ao mesmo tempo em que se faz uma corrente fluir entre 1 e 3. Isso significa dizer que:

$$Rs = \frac{V_{24}}{I_{13}} * 4,53$$

Com isso podemos preencher a tabela a seguir:

| Tipo | I <sub>13</sub> (A) | V <sub>24</sub> (V) | $R(\Omega)$ |

|------|---------------------|---------------------|-------------|

| N    |                     |                     |             |

| P    |                     |                     |             |

Tabela 1 – Resistência por quadrado

Outra medida a ser realizada é feita colocando-se uma corrente através de 4 e 6 e medindo-se a tensão entre 3 e 5. Utilizando-se o valor de resistência encontrado acima, podemos determinar a razão W/L, através da seguinte fórmula:

$$Rs = \frac{V_{35}}{I_{46}} * \frac{W}{L}$$

Assim podemos preencher a tabela abaixo:

| Tipo | I <sub>46</sub> (A) | $V_{35}(V)$ | W/L |

|------|---------------------|-------------|-----|

| N    |                     |             |     |

| P    |                     |             | _   |

Tabela 2 – W/L

### • Perguntas:

- i) Compare os valores obtidos na tabela 7 com os valores obtidos para o caco de teste durante o processamento?

- ii) Compare os valores obtidos para W/L na tabela 8 com o valor nominal de máscara, no caso de este estar disponível?

# 1.5) Flip-Flop

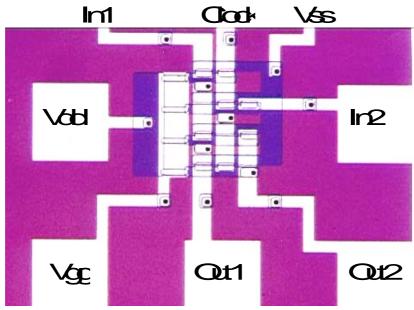

Em nosso chip fabricado, dentre as estruturas fabricadas, temos o seguinte flip-flop, cuja foto segue abaixo.

Figura 2 – Flip-Flop

Esse flip-flop é formado por 12 transistores p-MOS e a pinagem é a mostrada na figura acima.

A análise do flip-flop acima será feita através da injeção de níveis lógicos 0 (0V) e 1 (-5V) nas entradas Clock, In1 e In2, sendo Vgg colocado em -12V, Vdd em -5V e Vss em 0V. Realize essa análise conforme indica a tabela a seguir e preencha-a com os níveis lógicos obtidos nas saídas Out1 e Out2.

| Clock | In1 | In2 | Out1 | Out2 |

|-------|-----|-----|------|------|

| 0     | 0   | 0   |      |      |

| 0     | 0   | 1   |      |      |

| 0     | 1   | 0   |      |      |

| 0     | 1   | 1   |      |      |

| 1     | 0   | 0   |      |      |

| 1     | 0   | 1   |      |      |

| 1     | 1   | 0   |      |      |

| 1     | 1   | 1   |      |      |

Tabela 3 – Flip-Flop Teste – Tabela Verdade

### • Perguntas:

- i) Analisando os resultados obtidos na tabela 9, comente os mesmos e a partir disto descubra qual o tipo do Flip-Flop em questão.

- ii) Uma vez sabido o tipo do Flip-Flop em questão, descreva o seu circuito elétrico.