## Escalamento e Limites de Dispositivos MOS

Jacobus W. Swart

Leandro T. Manera

CCS e FEEC

UNICAMP

1

#### Sumário:

- 1. Introdução

- 2. Leis de escalamento

- 3. Limitações de Transistores Pequenas Dims.

- 1. Efeitos de canal curto: V<sub>T</sub> vs L

- 2. Efeito de canal estreito:  $V_T$  vs W

- 3. Punchthrough

- 4. Resistências parasitárias

- 5. Capacitância de porta

- 6. Corrente de tunelamento

- 7. Redução de mobilidade

- 8. Injeção de portadores quentes

- 9. Rupturas do transistor

- 4. Efeitos das limitações e "mapa de estrada".

- 5. Limites de Escalamento

2

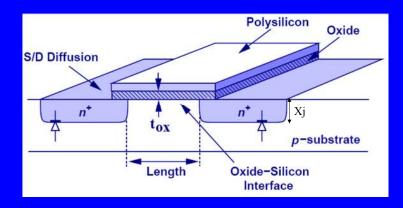

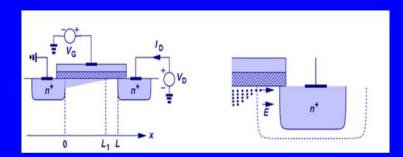

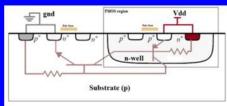

#### **Transistores MOSFET**

➤ A porta do transistor pode ser formado por polisilício ou outros tipos de materiais condutores (metais).

#### **Transistores MOSFET**

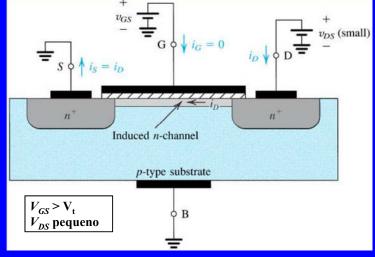

$\succ$  Transistor funciona como um resistor linear cujo valor é controlado por  $V_{GS}$

#### **Transistores MOSFET**

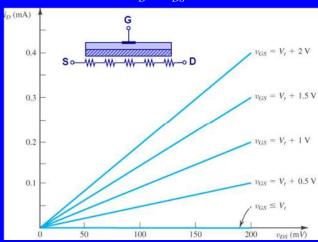

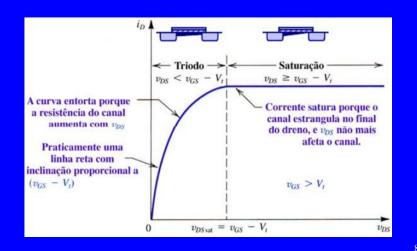

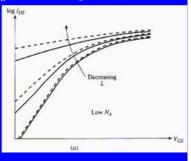

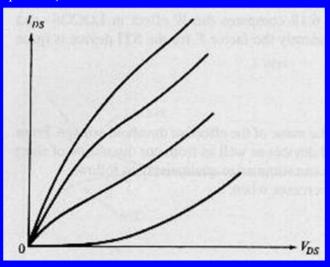

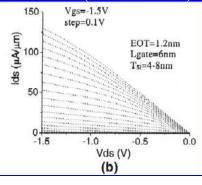

Curva característica  $i_D$  x  $v_{DS}$  – Transistor nMOS

$\succ$  Transistor funciona como um resistor linear cujo valor é controlado por  $V_{GS.}$

#### **Transistores MOSFET**

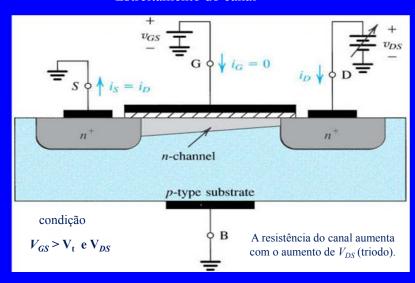

Estreitamento do canal

#### **Transistores MOSFET**

Estrangulamento do canal (pinch off) e modulação comprimento do canal (efeito canal curto)

Saturação

#### **Transistores MOSFET**

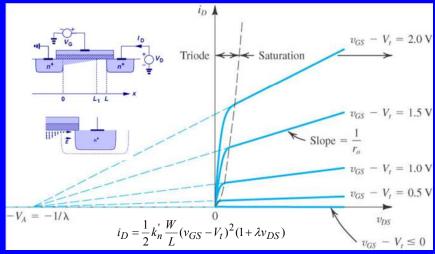

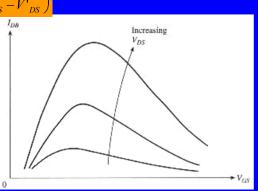

Curva característica  $i_D \times v_{DS}$  – Transistor nMOS

#### **Transistores MOSFET**

Curva característica  $i_D \times V_{DS}$ — Transistor nMOS

$v_{DS} \ge v_{GS} - V_t$

Saturation region

$$= k_n' \frac{W}{L} \left[ (v_{GS} - V_t) v_{DS} - \frac{1}{2} v_{DS} \right]^{2}$$

$$i_D = \frac{1}{2} k_n' \frac{W}{L} (v_{GS} - V_t)$$

Modulação do comprimento do canal

$\triangleright$  A corrente no canal aumenta com o aumento de  $v_{DS}!!$

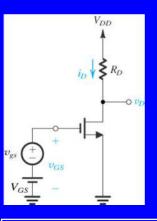

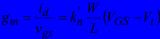

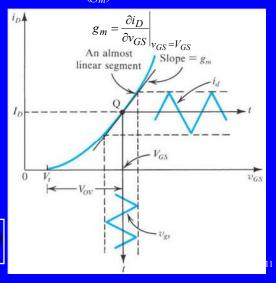

#### **Transistores MOSFET**

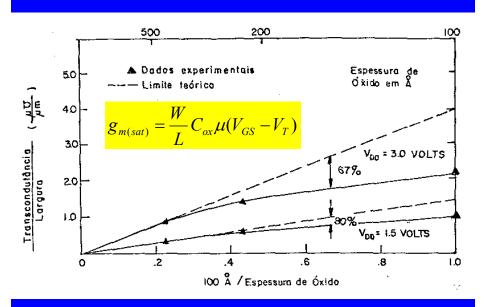

Transcondutância  $(g_m)$

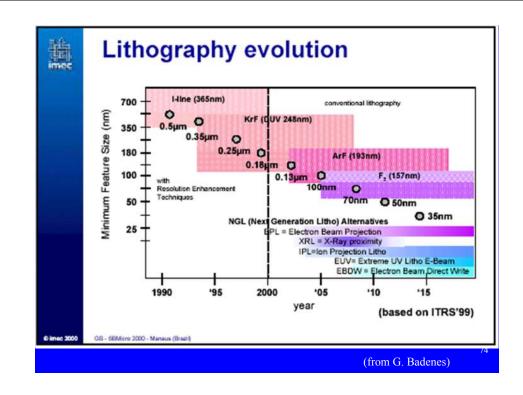

#### 1. Introdução - Escalamento

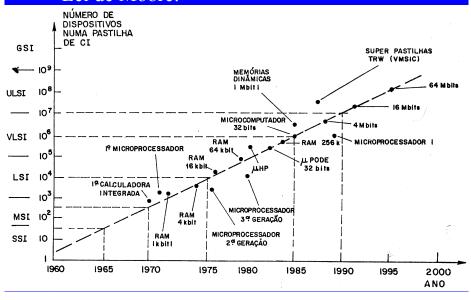

• Lei de Moore:

#### 1. Introdução – Escalamento – cont.

- Quais as forças propulsoras para o escalamento?

- Maior densidade integração ⇒ economia

- Menor consumo de energia ⇒ desempenho

- Maior velocidade de operação ⇒ desempenho

- Menor no. de chips / sistema ⇒ economia

14

#### 1. Introdução – Escalamento – cont.

- Perguntas:

- Como reduzir (escalar) dimensões?

- Quais as limitações dos dispositivos escalados?

- Quais os limites de escalamento?

#### 1. Introdução – Escalamento – cont.

| FEATURE             | LIMIT                  | REASON                         |

|---------------------|------------------------|--------------------------------|

| Oxide Thickness     | 2.3 nm                 | Leakage (I <sub>GATE</sub> )   |

| Junction Depth      | 30 nm                  | Resistance (R <sub>SDE</sub> ) |

| Channel Doping      | V <sub>T</sub> =0.25 V | Leakage (I <sub>OFF</sub> )    |

| SDE Under Diffusion | 15 nm                  | Resistance (R <sub>INV</sub> ) |

| Channel Length      | 0.06μm                 | Leakage (I <sub>OFF</sub> )    |

| Gate Length         | 0.10μm                 | Leakage (I <sub>OFF</sub> )    |

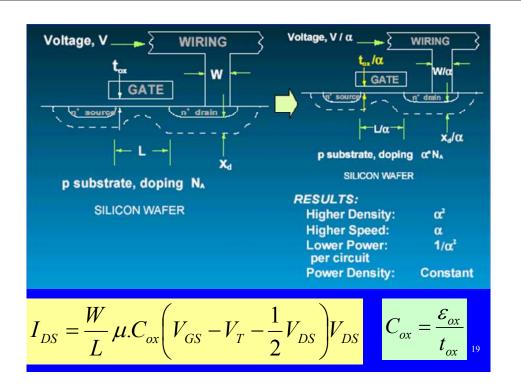

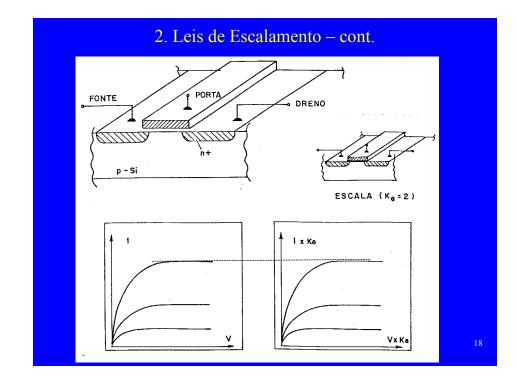

#### 2. Leis de Escalamento

Regra Escalamento por Campo elétrico Constante - EC

| Parâmetro             | Fator de escala(ke>1) |

|-----------------------|-----------------------|

| Dimensões:            | 1/k <sub>e</sub>      |

| $L, W, t_{ox}, x_{J}$ |                       |

| N dopagem             | k <sub>e</sub>        |

| Tensões               | 1/k <sub>e</sub>      |

Evita-se variações em efeitos que dependam do campo elétrico 17

#### 2. Leis de Escalamento – Tipos de Leis

| Parâmetro         | EC               | VC          | VQC         | Geral                  |

|-------------------|------------------|-------------|-------------|------------------------|

| $W, L, x_J$       | 1/k              | 1/k         | 1/k         | $1/k_d$                |

| $t_{OX}$          | 1/k              | 1/√k        | 1/k         | 1/k <sub>d</sub>       |

| N                 | k                | k           | k           | $k_d^2/k_v$            |

| $V_{\mathrm{DD}}$ | 1/k              | 1           | 1/√k        | $1/k_{\rm v}$          |

| $I_{DS}$          | 1/k              | √k          | 1           | $k_d/k_v^2$            |

| C                 | 1/k              | $1/k^{3/2}$ | 1/k         | 1/k <sub>d</sub>       |

| $t_a$             | 1/k              | $1/k^2$     | $1/k^{3/2}$ | $k_d/k_v^2$            |

| P                 | 1/k <sup>2</sup> | √k          | 1/√k        | $k_d/k_v^3$            |

| P.t <sub>a</sub>  | $1/k^3$          | $1/k^{3/2}$ | $1/k^2$     | $1/k_d^2k_v$           |

| P/A               | 1                | $k^{5/2}$   | $k^{3/2}$   | $k_d^{3}/k_v^{3^{20}}$ |

#### Três eras: i) tensão constante (70-90), ii) junções abruptas (90-00) e iii) strained Si engineering (00-...) Eras of Transistor Scaling Source/Drai Constant Voltage Scaling Technology Feature Size Abrupt Nominal 100nm Nanotechnology Strained 2010 1970 100 Source: Intel Technology Technology Voltage (V) (MV/cm) .7X Voltage E. Voltage Scaling 0.80 0.35 0.18 0.09 1990 2000 2010 1980 1.2

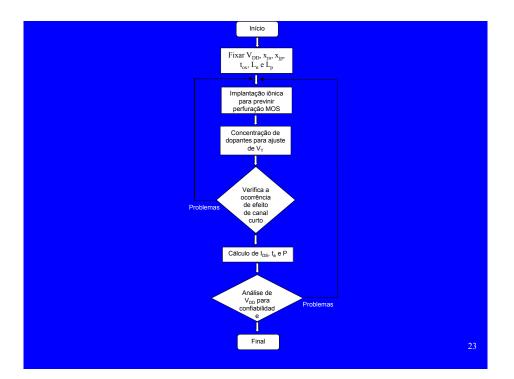

- Por simulações de:

- Processos (SUPREM; Athena)

- Dispositivos (PISCES; Atlas)

- Ajustar os parâmetros para ótimo desempenho, com análise de:

- Tensão de limiar, V<sub>T</sub>

- Efeito de canal curto (V<sub>T</sub> x L e V<sub>DD</sub>)

- Perfuração MOS (punchthrough)

- Corrente de corte, I<sub>off</sub>

- Tempo de atraso, t<sub>a</sub>

- Potência, P

- Corrente de porta e substrato p/ confiabilidade

#### 3. Limitações

#### Limitações de transistores de pequenas dimensões:

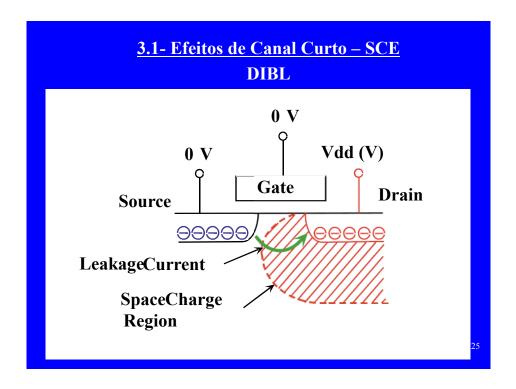

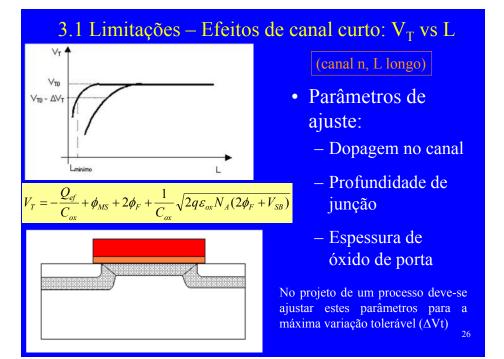

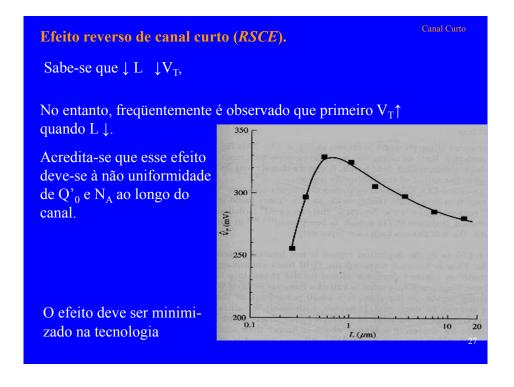

- 1. Efeitos de canal curto e canal estreito,  $\Delta V_T \times L \in \Delta V_T \times V_{DS}(DIBL)$

- 2. Perfuração MOS

- 3. Resistências parasitárias

- 4. Capacitância de inversão

- 5. Corrente de tunelamento de porta

- 6. Redução de mobilidade

- 7. Injeção de portadores quentes

- 8. Rupturas

24

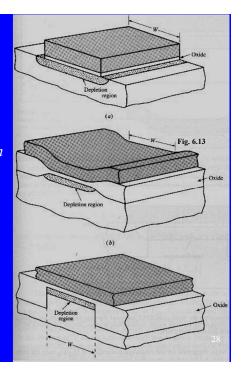

## 3.1 – <u>Dispositivos de canal</u> estreito.

Fig 6.13a – Largura ao longo do canal.

Fig.6.13b – LOCOS (local oxidation of silicon) – formação do "bico de passáro"

Fig 6.13c - STI (*shallow-trench isolation*) usado na tecnologia CMOS 0.35µm e abaixo.

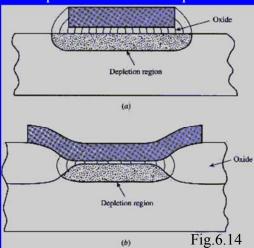

#### Isolação LOCOS.

A região de depleção não fica limitada pela área do óxido de porta.

Campos laterais originados de cada lado na porta terminam nos átomos ionizados.

Se W é grande, então uma pequena parcela da carga total é afetada pelos campos laterais.

Se W for pequeno, a parcela da carga afetada não é desprezível.

(a)

(b)

Neste caso, para depletar as cargas e formar uma camada de inversão, 20  $V_{GS}$  deve ser maior que previsto p/  $L \uparrow \Rightarrow V_T$  efetivo será  $\uparrow$

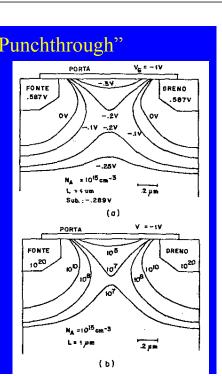

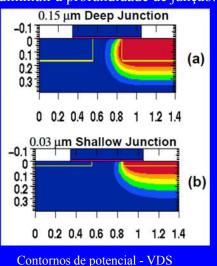

## 3.2 Limitações – "Punchthrough" DRENO SBTV DRENO .587 V -.2V N\_ = 10<sup>15</sup> cm-3 2 pm Latum Sub.:-.289 V V = -1V N<sub>A</sub> =10<sup>15</sup>cm-3

Nota: No caso STI é possível reduzir a dependência com W, pelo arredondamento da quina do Si do STI.

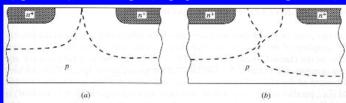

#### 3.2 Perfuração MOS (punchthrough).

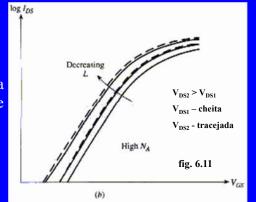

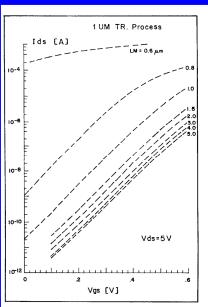

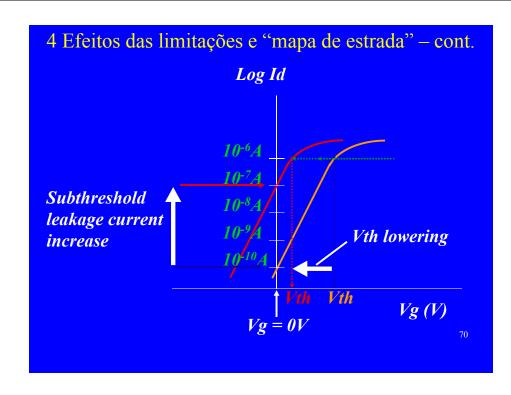

O critério mais usados para observar integridade dos efeitos eletrostáticos (canal curto) é S pouco dependente de V<sub>DS</sub> e com valor próximo ao L longo

$S = dV_{GS}/d \log I_{DS}$   $S \cong 80 \text{ mV/dec (longo) } e \cong 60 \text{ mV/dec (curto)}$

Para o menor dispositivo aceita-se uma variação de alguns % (~ 5 mV/dec)

A fig. 6.11b apresenta uma boa característica eletrostática.

Isolação LOCOS e STI

O deslocamento da curva para esquerda quando V<sub>DS</sub> ↑ deve-se ao efeito DIBL.

$\Delta V_{GS}/\Delta V_{DS} < 100 \text{ mV/V}$ valores típicos aceitáveis.

Fig 6.11a, grande dependência de S com V<sub>DS</sub> – efeito de perfuração MOS

É uma caso severo de diminuição de barreira que causa um fluxo de elétrons da fonte para o dreno. A integridade eletrostática é violada

Também pode ocorrer quando há o encontro das regiões de depleção da fonte e do dreno, na ausência da região de depleção na porta:

- a) perfuração de superfície (dopagem uniforme)

- b) perfuração de corpo (dopagem maior na superfície)

22

Efeitos de perfuração MOS sobre as curvas características:

Perfuração MOS deve ser evitado por construção e não necessita ser modelado em modelos compactos SPICE.

34

#### $\ \ \, \text{``Punchthrough''}-cont.$

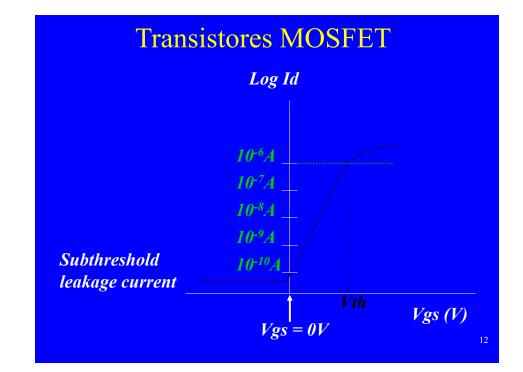

Para observar a ocorrência: Log Id x  $V_{GS}$  – não mais apresenta comportamento exponencial com  $V_{GS}$ .

- Parâmetros de ajuste:

- Dopagem no canal, com alta energia para elevar a conc. do corpo, evitar que a depleção do dreno caminhe para o canal

- Profundidade de junção (LDD ou SDE=Source/drain extention)

- Espessura de óxido de porta<sub>35</sub>

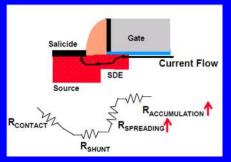

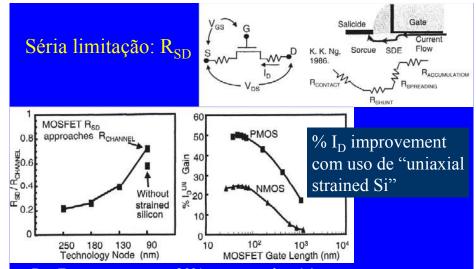

# 3.3 Limitações – Resistências Parasitárias Janela de Contato Porta Extensão de fonte/dreno

#### 3.3 Limitações – Resistências Parasitárias

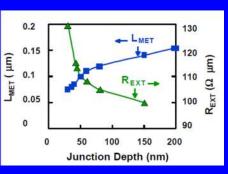

Compromisso entre aumento da corrente de dreno e aumento das resistências parasitárias.

#### 3.3 Limitações – Resistências Parasitárias – cont.

Para diminuir efeitos de canal curto deve-se

diminuir a profundidade de junção.

Dificuldades:  $X_J \downarrow \Rightarrow R_d \uparrow$ Área  $\downarrow \Rightarrow R_{Co} \uparrow$

30

#### 3.3 Limitações – Resistências Parasitárias – cont.

- Dificuldades:

- $X_J \downarrow \Rightarrow R_d \uparrow$

- Área  $\downarrow$  ⇒  $R_{Co}$  ↑

- Soluções:

- Siliceto sobre a região de S/D

- − S/D com alta dopagem, uso de RTP.

- Perfil abrupto da região LDD:  $R_{SP}$  e  $R_{AC}$   $\downarrow$

Recomenda-se que a soma das resistências parasitarias de fonte e dreno não excedam a 10% da resistência intrínseca do canal

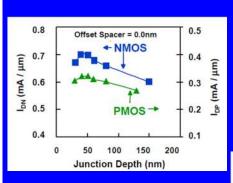

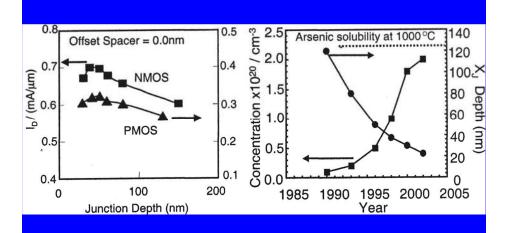

#### I<sub>on</sub> vs. x<sub>J</sub> para I<sub>off</sub> fixo (Era junção abrupta)

$X_J$  menor resulta S menor, permite  $V_T$  menor, aumenta  $I_{on}$

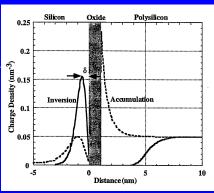

#### 3.4 Limitações – Capacitância de Porta

- Classicamente:  $Q_c = C_{ox}(V_{GS} V_T)$

- • Correções:

$$\frac{1}{C_{ef}} = \frac{1}{C_{ox}} + \frac{1}{C_{c}} + \frac{1}{C_{poli}}$$

$$C_c = \frac{\mathcal{E}_{Si}}{t_c}$$

$$C_{poli} = rac{\mathcal{E}_{Si}}{t_{depl}}$$

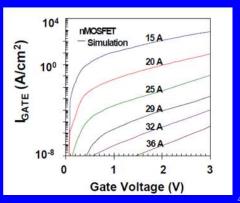

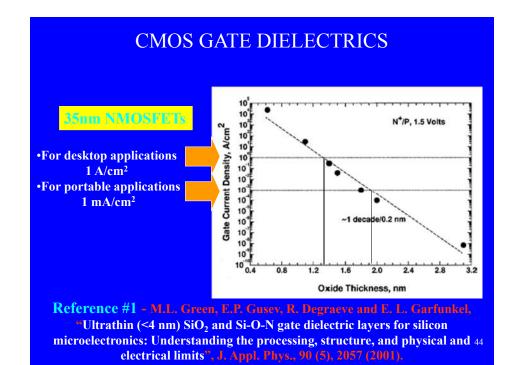

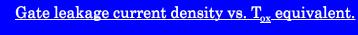

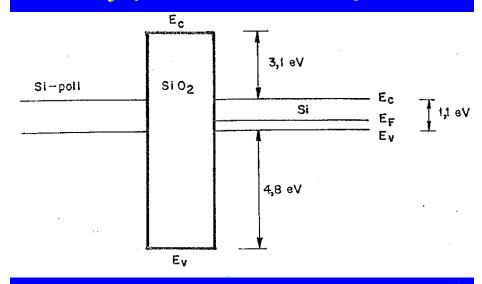

#### 3.5 Limitações – Corrente de tunelamento

O limite da espessura do óxido não está limitado pelo processo de fabricação. Pode –se fabricar SiO<sub>2</sub> < 1,5nm Limitado por corrente de fuga/tunelamento!

#### 3.5 Limitações – Corrente de tunelamento

$$J_{tun} = A.\exp(-2\sqrt{\frac{2.m^*.q.\phi_B}{\hbar^2}}.t_{ox})$$

- $I_{\text{tunel}} < 0.01 I_{\text{DS}}$

- $SiO_2 > \sim 1,5 \text{ nm}$

- Solução: usar dielétrico de alta constante dielétrica:

- Espessura maior para mesma capacitância!

- Necessário para L < ~ 50 nm.

~ 2005: L ~ 50 nm Necessidade de high-k, p/ potência reduzida

T. Ghani et al., Symp. on VLSI, p.174, June, 2000<sub>45</sub>

###

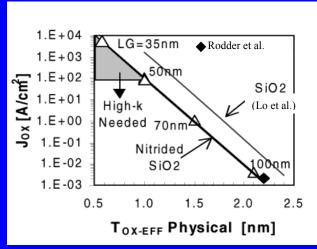

Saturação da velocidade dos portadores  $\sim 10^7 \text{cm/s}$ . Campo elétrico  $2x10^4$  para n e  $1x10^5$  para p

40

#### 3.6 Limitações – Redução de mobilidade

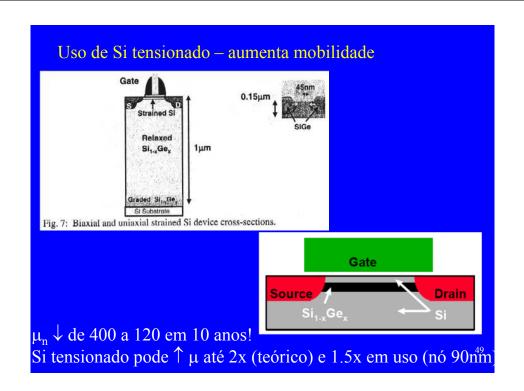

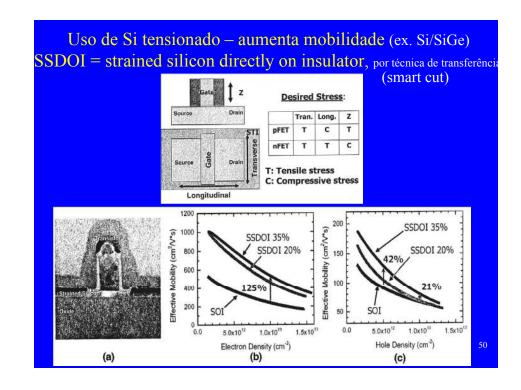

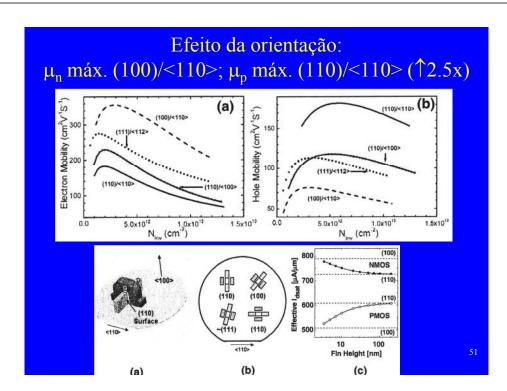

#### 3.6 Limitações – Redução de mobilidade – cont.

Transistores MOS com Ge (Stanford)

• Mobilidade muito melhor, porém, baixo limite de solubilidade sólida  $\sim 10^{19}$  cm<sup>-3</sup>.

- $R_{SD}/R_{ch}$  era menor que 20%, agora tende a 1!

- Ganho pelo strain tende a saturar para L<100nm (nMOS) e L<50nm (pMOS) devido à R<sub>SD</sub>.

- Prioridade: reduzir R<sub>SD</sub>; não adianta melhorar a chave MOS (CNT?)

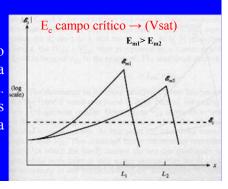

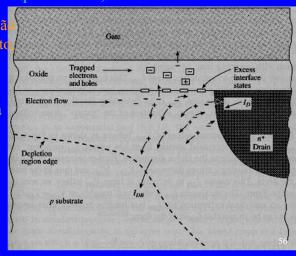

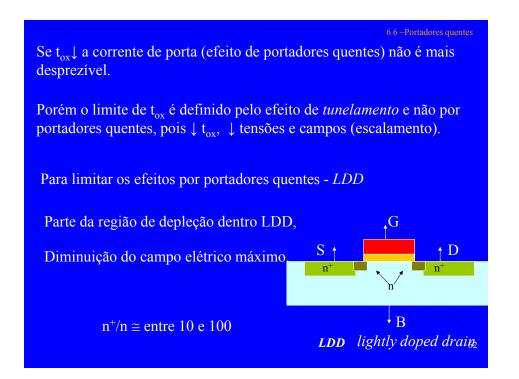

#### Portadores quentes.

O campo longitudinal aumenta da fonte para o dreno.

O pico do campo se dá na junção canal-dreno e depende fortemente de  $\,L\,e\,V_{DS}.$

Para  $L_{(2)}\uparrow$ , o campo crítico ~ coincide com o inicio do estrangulamento. Para  $L_{(1)}\downarrow$ , há uma porção do canal antes do estrangulamento onde a velocidade dos portadores satura.

#### Em campos $> E_c$ :

A velocidade dos portadores não aumenta devido às colisões, porém a energia cinética randômica aumenta. Uma pequena fração de portadores adquirem uma quantidade de energia alta  $\Rightarrow$  "portadores quentes"

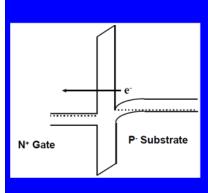

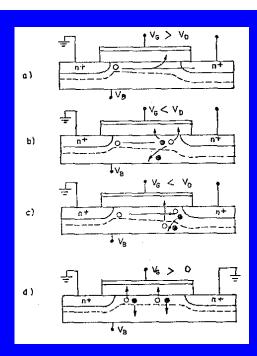

#### 3.7 Injeção de Portadores Quentes

Alguns do elétrons adquirem energia suficiente para produzir ionização por impacto com átomos de silício do cristal, onde são criados novos pares elétron-lacuna  $\Rightarrow$  avalanche fraca.

Elétrons gerados são atraídos para o dreno;

Lacunas geradas sã "puxadas" para o substrato gerando a corrente  $I_{DB}$ .

Uma fração dos elétrons podem sobrepor a barreira do SiO<sub>2</sub>, serem injetados no óxido e coletados pela porta.

$\Rightarrow \uparrow N_{it}$  e modifica  $Q_0$ ,  $\Rightarrow \downarrow$ tempo de vida dos dispositivos e  $\Delta Vt$

#### 3.7 Injeção de Portadores Quentes – cont.

- Modos principais de injeção de portadores quentes:

- a) elétrons quentes do canal

- b) elétrons quentes e lacunas quentes produzidos por avalanche;

- c) elétrons quentes do substrato, induzidos por ionização secundária;

- d) elétrons térmicos quentes.

57

-58

#### 3.7 Injeção de Portadores Quentes – cont.

- Efeitos da injeção de portadores quentes:

- Corrente de porta

- Corrente de substrato

- Degradação da mobilidade ou transcondutância

- Degradação da tensão de limiar

- Ruptura do transistor

- Latch-up em CMOS.

#### 3.7 Injeção de Portadores Quentes – cont.

- Dependência com parâmetros:

- a) polarizações  $V_G$ ,  $V_D$ ,  $V_B$ ;

- b) dimensões L,  $t_{ox}$ ,  $X_i$ ;

- c) dopagem de substrato;

- d) forma do perfil do dreno próximo ao canal;

- e) temperatura.

- Soluções:

- − a) Reduzir tensões (adotado após 1990)

- b) Alterar dopagem de S/D: LDD ou extensão (usado durante década de 80; em seguida, a extensão foi projetada para desempenho, I<sub>on</sub>/I<sub>off</sub>).

Ĭ

6.6 –Portadores quente

$I_{DB} \ \alpha \ I_{DS} \qquad I_{DB} \ \acute{e} \ função \ do \ campo, \ ou, \ excesso \ V_{DS} \mbox{-}V'_{DS}$

Para um dado  $V_{DS}$  e aumentando  $V_{GS}$ ,  $\uparrow I_{DS}$  e  $\uparrow I_{DB}$

aumentando mais  $V_{GS}$ ,  $\uparrow V'_{DS}$  e  $(V_{DS}$  -  $V'_{DS}) \downarrow \,$  e o campo no dreno  $\downarrow$

$$|I_{DB}| = |I_{DS}|K_i(V_{DS} - V'_{DS}) \exp\left(\frac{V_i}{V_{DS} - V'_{DS}}\right)$$

K<sub>i</sub> de 1 a 3 V<sub>i</sub> de 10 a 30V.

$I_{DB}$  é máx em  $V_{GS} \sim V_{DS}/2$

corrente total de dreno,

$$I_{D} = I_{DS} + I_{DB}$$

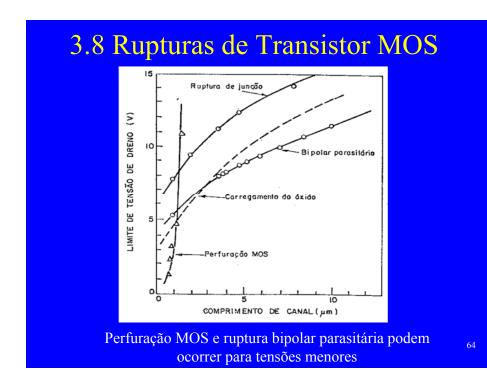

#### 3.8 Rupturas de Transistor MOS

A - Ruptura do óxido de porta: Emax =  $1x10^7$  V/cm | Limite era de ~1 a 1,5x10<sup>6</sup> V/cm | Atualmente 5x10<sup>6</sup> V/cm (modelamento do efeito de ruptura)

B - Ruptura bipolar parasitária: Corrente de substrato pode gerar polarização direta na junção fontesubstrato.

C - Ruptura por avalanche de dreno e/ou canal: pode haver ruptura devido á multiplicação de portadores por avalanche.

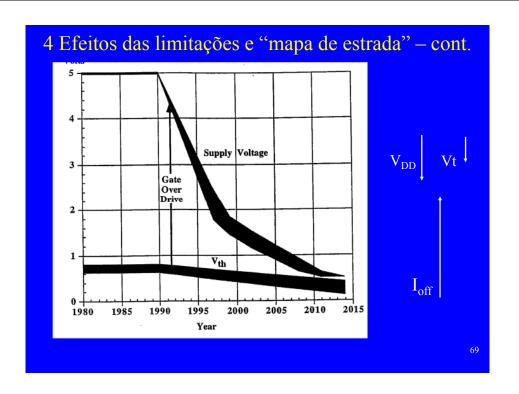

## 4. Efeitos das limitações e "mapa de estrada"

- As limitações estudadas:

- a) afetam o desempenho elétrico dos dispositivos

- b) determinam as condições limites de operação

- c) determinam condições de contorno para o projeto da estrutura física dos transistores e do processo de fabricação.

65

#### ITRS 2001 with 2002 Update

#### **Roadmap CMOS**

http://www.itrs.net/2001\_sia\_roadmap/home.htm

| Ano | 01  | 02  | 03  | 04 | 05 | 06 | 07 | 10 | 13 | 16 |

|-----|-----|-----|-----|----|----|----|----|----|----|----|

| P1  | 130 | 115 | 100 | 90 | 80 | 70 | 65 | 45 | 32 | 22 |

| P2  | 150 | 130 | 107 | 90 | 80 | 70 | 65 | 45 | 32 | 22 |

| L1  | 90  | 75  | 65  | 53 | 45 | 40 | 35 | 25 | 18 | 13 |

| L2  | 65  | 53  | 45  | 37 | 32 | 28 | 25 | 18 | 13 | 9  |

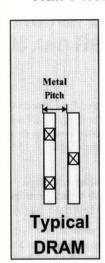

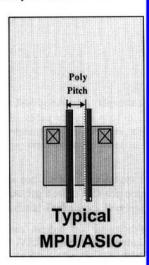

P1 = DRAM ½ Pitch;

$P2 = MPU \frac{1}{2}$  Pitch

L1 = PMU Printed Gate Lenght;

L2 = PMU Physical Gate Lenght; (all in nm)

66

#### ITRS 2001 with 2002 Update

#### Half Pitch (=Pitch/2) Definition

ITRS2001 – dimensões em nm 13 16 19 22 Ano 04 07 65 32 22 10 90 45 Lito 35 53 25 18 **Printed Gate** 13 6 37 25 18 13 Physical Gate 9

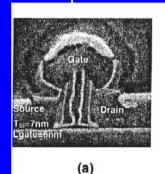

Transistor pMOS com L = 6 nm (IBM - 2004)

68

7

#### 4. Efeitos das limitações e "mapa de estrada" – cont.

| Ano                                 | 1997    | 1999                | 2002                | 2005                | 2008               | 2011                 | 2014                 |

|-------------------------------------|---------|---------------------|---------------------|---------------------|--------------------|----------------------|----------------------|

| Dimensão mínima (nm)                | 250     | 180                 | 130                 | 100                 | 70                 | 50                   | 35                   |

| DRAM (início de vendas)             | 256M    | 1G                  | (3G)                | 8G                  | (24G)              | 64G                  | (192G)               |

| Área chip DRAM (mm²)                | 280     | 400                 | 460                 | 530                 | 630                | 710                  | 860                  |

| Espessura equivalente de            | 3-5     | 1.9-2.5             | 1.5-1.9             | 1.0-1.5             | 0.8-1.2            | 0.6-0.8              | 0.5-0.6              |

| óxido (nm)                          |         |                     |                     |                     |                    |                      |                      |

| Res. máx. de material de            |         | 60                  | 43                  | 33                  | 23                 | 16                   | 11                   |

| porta (μΩ.cm)                       |         |                     |                     |                     |                    |                      |                      |

| Res máx. de contato                 |         | 30x10 <sup>-8</sup> | 17x10 <sup>-8</sup> | 10x10 <sup>-8</sup> | 5x10 <sup>-8</sup> | 2.5x10 <sup>-8</sup> | 1.5x10 <sup>-8</sup> |

| siliceto/si (Ω.cm²)                 |         |                     |                     |                     |                    |                      |                      |

| Resistência de folha da             |         | 350-                | 250-                | 200-                | 150-               | 120-                 | 100-                 |

| extensão S/D (Ω/□)                  |         | 800                 | 700                 | 625                 | 525                | 525                  | 400                  |

| X <sub>J</sub> da extensão S/D (nm) | 50-100  | 42-70               | 25-43               | 20-33               | 16-26              | 11-19                | 8-13                 |

| Perfil da extensão S/D              |         | 14                  | 8.5                 | 6.5                 | 4.5                | 3.2                  | 2.2                  |

| (nm/dec.)                           |         |                     |                     |                     |                    |                      |                      |

| $V_{DD}$                            | 1.8-2.5 | 1.5-1.8             | 1.2-1.5             | 0.9-1.2             | 0.6-0.9            | 0.5-0.6              | 0.5                  |

| <u>An</u>               | **                     |                      |       |                         |

|-------------------------|------------------------|----------------------|-------|-------------------------|

|                         | 1972                   | 2001                 | Ratio | Limiting factor         |

| Gate length             | 6 μm                   | 0.1 μm               | 1/60  |                         |

| Gate oxide              | 100 nm                 | 2 nm                 | 1/50  | Gate leakage<br>TDDB    |

| Junction depth          | 700 nm                 | 35 nm                | 1/20  | Resistance              |

| Supply voltage          | 5 V                    | 1.2 V                | 1/4   | Vth, Power              |

| Threshold voltag        | ge 0.8 V               | 0.3 V                | 1/2.6 | Subthreshold<br>leakage |

| Electric field (Vd/tox) | 0.5 MVcm <sup>-1</sup> | 6 MVcm <sup>-1</sup> | 30    | TDDB                    |

|                         |                        |                      |       | (from H. Iwai) 75       |

## Carbon NanoTube (CNT) FET

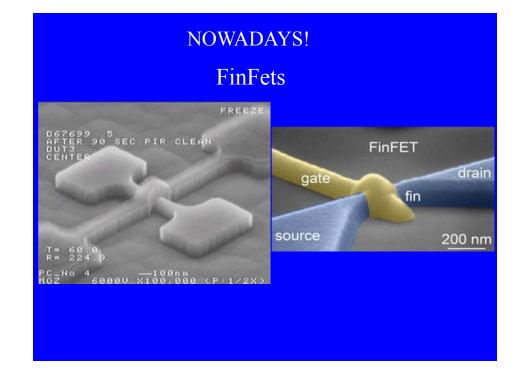

#### **NOWADAYS!**

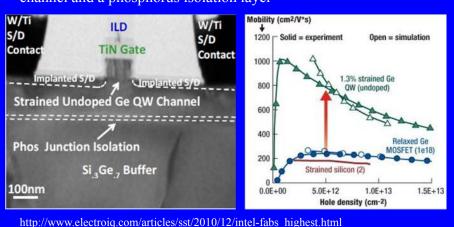

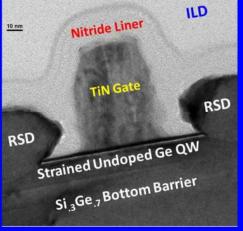

Intel announced a record-breaking quantum well field effect transistor (QWFET); a 35nm gate length device capable of 0.28mA/μm drive current and peak transconductance of 1350μS/μm. These QWFETs used InGaAs as the quantum well channel material. High-mobility germanium QWFET that achieves the highest mobility (770 cm²/Vsec) with ultrathin oxide thickness (14.5Å) for low-power CMOS applications.

http://www.electroiq.com/articles/sst/2010/12/intel-fabs highest.html

#### **NOWADAYS!**

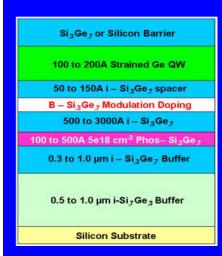

The transistor uses HfO<sub>2</sub>/TiN high-k/metal gate, self-aligned boron implanted source and drains, W/Ti contacts, 1.3% strained Ge QW channel and a phosphorus isolation layer

#### NOWADAYS!

##

#### Limites Teóricos

Limite das flutuações térmicas:  $\Delta\epsilon > 4kT$ . Qualquer informação deve conter no mínimo 4kT.

$$\Delta V = 4kT/q$$

Sabe-se que o tempo de atraso mínimo :

$$\tau_{\min} = \frac{L_{\min}}{v_{\max}} + \frac{\Delta V / EC}{v_{\max}}$$

#### Para o silício:

Ec =

$$3x10^5$$

V/cm<sup>3</sup>,  $v_{max} = 1x107$  cm/s, Lmin =  $10$  nm (?)

$\therefore \tau = 3x10^{-14}$  s ou  $\sim 5$  THz